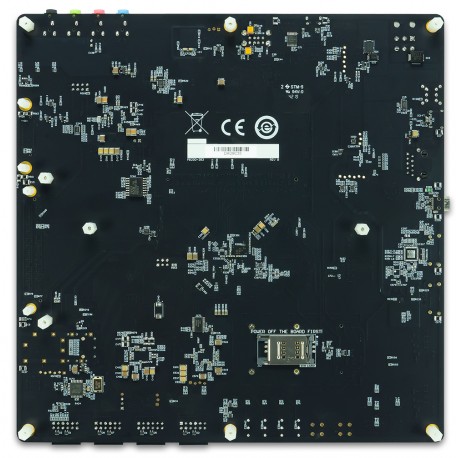

Carte de développement Genesys ZU-3EG : Zynq Ultrascale+ MPSoC

Dont 0,24 € d'eco-participation déjà incluse dans le prix

La Genesys ZU-3EG est une carte de développement autonome optimisées en interfaces multimédia et connectivité réseau, dont la bibliothèque de documentation très complète vous permettra de développer rapidement des applications d'IA, de recherche, de dispositifs dans le domaine de l'aérospatiales, de la défense, du cloud computing et de la vision intégrée.

Le Xilinx Zynq UltraScale + MPSoC au cœur de la carte Genesys ZU-3EG offre une informatique hétérogène avec son ARM A-53 APU et ARM Mali-400 MP2 GPU pour aller de pair avec une interface mémoire substantielle.

Un connecteur Type-C complet avec USB 3.0 et USB 2.0 (Dual-Role-Data et Dual-Role-Power), un transceiver Gigabit intégré prenant en charge la DDR4 ainsi que des port USB Type-C 3.1, PCIe, SATA et DisplayPort sont également présents sur la carte.

La carte Genesys ZU-3EG prend en charge plusieurs entrées de caméras, un codec audio intégré, la vidéo 4 K, le WiFi ainsi qu'une connexion Ethernet 1G dans une plate-forme basée sur Linux, constituant un kit de développement complet qui excelle dans la 5G, la radio cellulaire (WWAN), le SSD, l'infrastructure radio sans fil et la vidéo pour des applications dans les domaines de la surveillance, du streaming et de l'encodage.

La carte Genesys ZU-3EG dispose de connecteurs au format Digilent Pmod et ainsi que des ports Zmod haute vitesse utilisant la nouvelle norme SYZYGY d'Opal Kelly, qui s'associe à la nouvelle famille de module Zmod de Digilent permettant l'utilisation d'entrées/sorties hautes performances (idéal pour les applications de radio logiciel, de gestion d'ultrasons et autres systèmes d'acquisition de données ou de traitement du signal).

Documentations:

- Datasheet de la carte

Liens démo / projets:

- Installation des fichiers Vivado, Xilinx SDK et Digilent Board

Remarque: Lors de l'installation de Vivado, assurez-vous d'inclure la prise en charge des Zynq Ultrascale +.

Remarque: les projets Digilent pour Genesys ZU ne sont actuellement pris en charge que dans Vivado 2019.1

- Premiers pas avec Vivado IP Integrator

Remarque: Ce guide a été initialement écrit pour les cartes Zynq non Ultrascale et les cartes utilisant Microblaze.

Le flux pour Ultrascale Zynq est en grande partie le même que non-Ultrascale Zynq. Le noyau IP «Zynq Ultrascale + MPSoC» doit être utilisé à la place du «système de traitement ZYNQ7»

- Projet Vivado prêt à l'emploi Genesys ZU

- Projet Petalinux prêt à l'emploi de Genesys ZU

Caractéristiques:

- XCZU3EG-1SFVC784E (avec dissipateur thermique et ventilateur)

o Unité de traitement des applications ARM® Cortex-A53 quadricœur

o Unité de traitement en temps réel ARM® Cortex-R5 bicœur

o Unité de traitement graphique Mali-400 MP2

o Cellules logiques 154K

- Mémoire :

o Module SODIMM DDR4 4 Go

o Flash ISSI 256 Mo SNOR

o Emplacement pour carte MicroSD™

- Connectivité périphérique:

o Périphérique double rôle USB Type-C 3.1 Gen1

o Double emplacement MiniPCIe / mSATA

o Hôte USB 2.0 · Connectivité réseau:

o 2,4 GHz Wi-Fi embarqué

o 1 G avec Ethernet IEEE 1588

o Emplacement pour carte SIM

o WLAN / WWAN / LoRa: option - MiniPCIe

- Multimédia:

o 1.2a Port d'affichage à double voie

o 2x Pcam à double voie

o Codec audio · Extension:

o 1x FMC connecteur d'extension

o 1x port SYZYGY

o 4x ports Pmod

- GPIO: LED, boutons, commutateurs

Contenu livré:

- Alimentation 12 V / 8 A, avec connecteur PCIE

- Câble IEC, EU, 1,2 mètre

- Câble USB A vers MICRO B

- Câble USB A à Type C 15 cm

- JTAG HS1

- Voucher pour cœurs IP Xilinx MIPI CSI-2

Produits associés