- 1602 views

Traduction du document écrit par Mr Pablo Trujillo (*)

La détection de tonalités uniques ou d'harmoniques reste un défi pour les systèmes embarqués, car elle nécessite une grande puissance de calcul. Les concepteurs peuvent facilement évaluer différentes approches en utilisant des cartes FPGA pour la génération de signaux et la détection de tonalité.

Les ingénieurs doivent parfois mettre en œuvre rapidement un système de validation de principe. Et les kits et modules d'évaluation, parfaitement adaptés à l'application considérée, ne sont pas toujours disponibles. C'est particulièrement le cas si une logique discrète et une puissance de calcul élevée sont nécessaires en même temps. C'est là que les cartes de développement avec FPGA peuvent aider. Par exemple, un concepteur doit évaluer la détection de tonalités uniques spéciales dans un signal, ce qui reste un défi pour le matériel et la puissance de traitement des systèmes embarqués. Pour accomplir cette tâche, il peut générer le signal sur une carte et l'analyser sur une seconde.

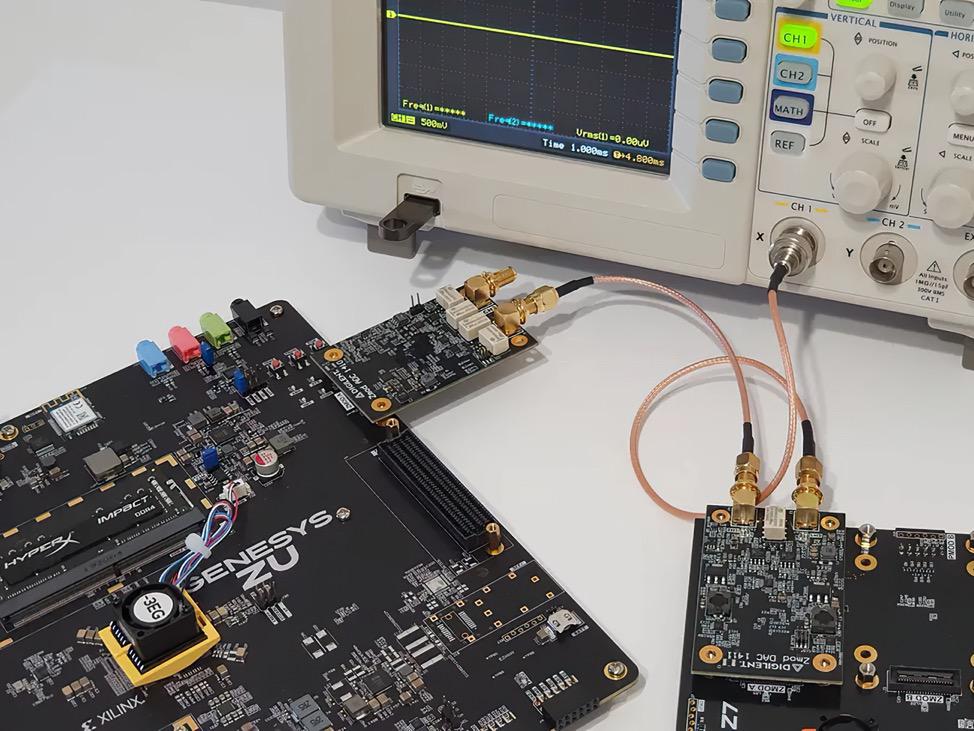

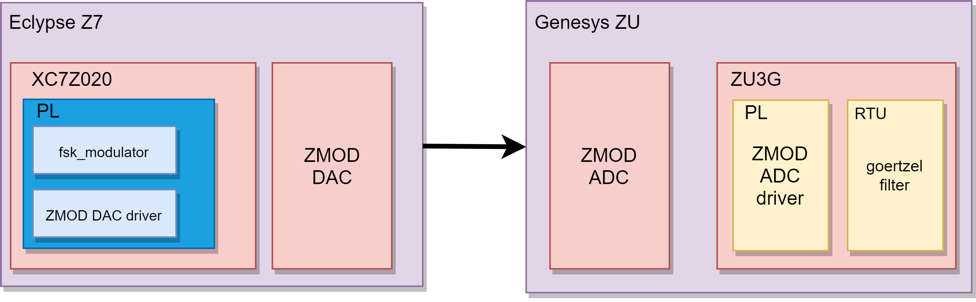

L'utilisation de deux cartes de développement FPGA, qui sont connectées via le signal analogique, accomplira cela facilement. Pour la carte créant le signal à une seule tonalité, une carte Eclypse Z7 Zynq-7000 APSoC (All Programmable System-on-Chip) ainsi que le module convertisseur numérique-analogique Zmod DAC 1411, tous deux conçues par la société Digilent, pourraient être utilisées. Un générateur de signal fonctionnant sur la carte Eclypse créerait alors le signal en utilisant une modulation par déplacement de fréquence, ce qui est courant dans les systèmes de communication.

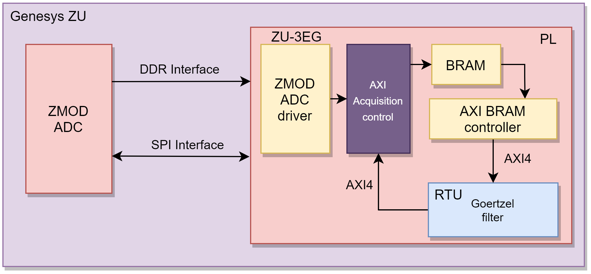

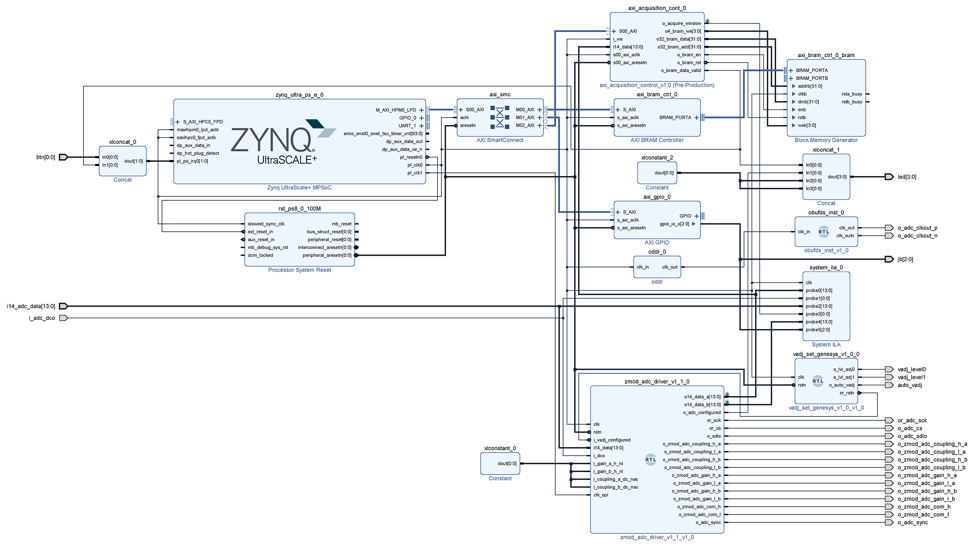

Côté réception, la carte de développement Genesys ZU-3EG Zynq Ultrascale+ MPSoC de Digilent et le module convertisseur analogique-numérique Zmod ADC 1410 pour l'acquisition du signal sont un excellent choix. Le système sur puce (MPSoC) multiprocesseur embarqué de Genesys ne comprend pas seulement une unité de traitement d'applications Arm Cortex-A53 à quatre cœurs. Il comprend également une unité de traitement en temps réel (RPU) Arr Cortex-R5F à double cœur et de nombreuses logiques programmables (PL). De cette façon, une puissance de traitement suffisante est disponible pour la tâche à accomplir.

Implémentation de la génération de tonalité avec un modulateur FSK

La technique de modulation FSK module une fréquence porteuse sinusoïdale avec différentes fréquences pour coder soit un "0" logique, soit un "1" logique. Comme il fonctionne avec une bande de fréquences, il est possible non seulement de coder des valeurs binaires mais aussi des octets complets. Le récepteur décoderait alors le signal analogique résultant avec une transformation de Fourier rapide (FFT), une transformation de Fourier discrète (DFT) ou un filtre de Goertzel.

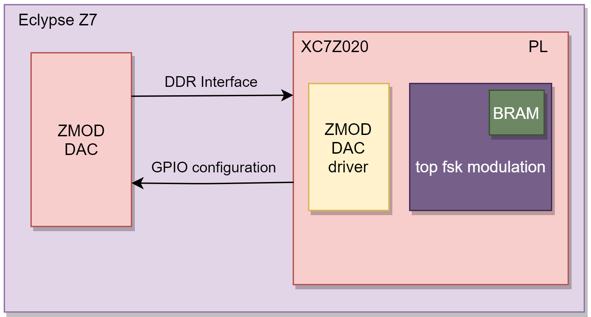

Pour atteindre les hautes fréquences requises du signal de sortie, un signal d'horloge rapide est nécessaire. La carte Eclypse dispose de deux sources d'horloge connectées au Zynq APSoC : l'une directement au sous-système de traitement (PS) et l'autre provenant du PHY Ethernet à la logique programmable (PL). Comme le PS n'est pas nécessaire pour créer le signal modulé, l'horloge connectée au PL qui fonctionne à une fréquence de 25MHz peut être utilisée. Pour obtenir des fréquences plus élevées, par exemple 100 MHz, l'un des gestionnaires d'horloge en mode mixte (MMCM) peut être utilisé. Ceux-ci font partie de la tuile de gestion d'horloge (CMT) sur l'architecture UltraScale.

Le signal porteur pour le FSK est stocké sous forme d'onde sinusoïdale dans l'une des mémoires à accès aléatoire par blocs (BRAM) du SoC. À chaque front de l'horloge, une valeur d'une adresse dans la BRAM sera lue et l'adresse incrémentée. Il est possible de créer les différentes fréquences liées aux niveaux logiques à coder en utilisant différentes valeurs d'incrément.

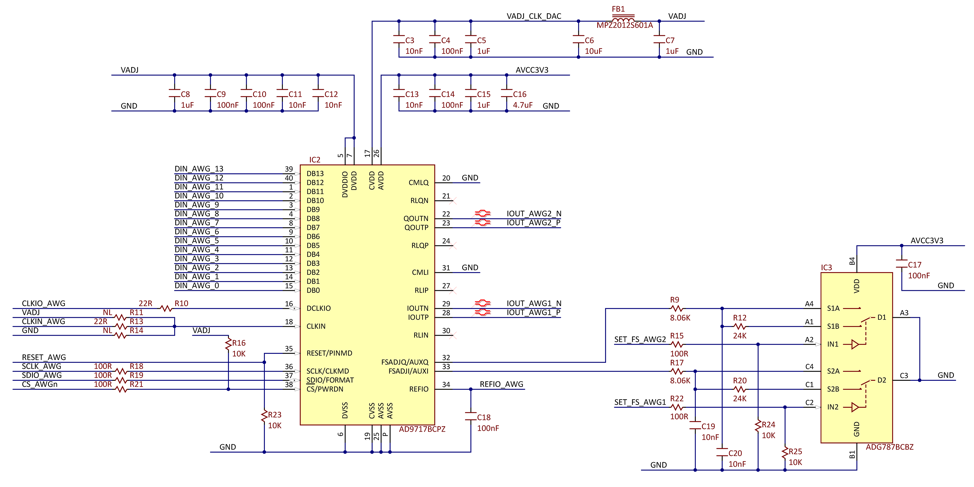

Avant que le signal modulé puisse être converti dans le domaine analogique, le convertisseur numérique-analogique sur le module Zmod DAC doit être configuré. Cela se fait en réglant le circuit intégré du multiplexeur analogique sur la carte à la valeur requise.

Détection d'une seule tonalité avec l'algorithme de Goertzel

Le signal analogique est ensuite acquis par le convertisseur analogique-numérique d'un module ADC Zmod monté sur une carte Genesys ZU. La carte ADC Zmod utilise le convertisseur AD9648 d'Analog Devices. Il a une résolution de 14 bits, deux canaux et fournit 105 MSamples/sec. La carte doit être configurée et l'alimentation activée au démarrage. Un module disponible gratuitement créé par Digilent pour une utilisation sur le FPGA prendra en charge ces tâches. Le Zmod se connecte à la carte de développement Genesys ZU via l'interface compatible SYZYGY via un port SPI et une interface DDR pour le transfert de données.

Pour créer cette interface DDR sur les appareils Zynq UltraScale+, les primitives IDDRE1 (registre d'entrée à double débit de données dédié 1) doivent être utilisées. Ces primitives sont similaires aux primitives IDDR de la série 7 de Xilinx, mais elles sont incompatibles avec les nouvelles générations. Pour permettre la communication, le sous-système de traitement doit générer deux signaux d'horloge : un pour les transferts sur le port SPI à 50MHz et un pour l'interface DDR et les modules AXI (Advanced extensible interface) pour le contrôle et BRAM à 100MHz. Cette fréquence correspond également à la fréquence d'échantillonnage.

Une fois tous les échantillons lus et déplacés vers la BRAM, l'algorithme de Goertzel s'exécutera pour détecter si les fréquences en question sont présentes dans le signal. Alors qu'il serait possible d'utiliser une FFT pour découvrir la présence d'une seule tonalité dans une séquence temporelle de n échantillons, elle n'est pas très efficace, car plusieurs multiplications de nombres complexes devraient être exécutées. L'emploi d'une DFT à point unique réduirait le nombre de multiplications et serait donc plus efficace. Mais cela ne résout toujours pas le problème des opérations sur les nombres complexes.

L'algorithme de Goertzel en revanche est très efficace. Il est implémenté sous la forme d'un filtre IIR de second ordre (réponse impulsionnelle infinie) utilisant deux coefficients de rétroaction réels et un seul coefficient d'anticipation complexe, réduisant le nombre de calculs arithmétiques. Sur la carte Genesys ZU, l'algorithme s'exécutera sur l'unité de traitement en temps réel Arm Cortex-R5F du MPSoC Zynq embarqué.

Le filtre a besoin d'un nombre statique d'échantillons pour calculer la tonalité sélectionnée. Ces échantillons doivent être partagés entre la logique programmable et le sous-système de traitement. Une solution proposée par Digilent consiste à utiliser un bloc IP AXI qui lit un nombre configurable de valeurs converties et les écrit dans la BRAM. Cette mémoire vive de bloc doit être créée comme une véritable mémoire à double port, où un port est connecté au module de contrôle d'acquisition AXI et l'autre au contrôleur AXI BRAM. Le module de contrôle AXI ne contiendra que deux registres : un pour le démarrage de l'acquisition et l'autre pour le réglage de la longueur de la fenêtre.

La figure 6 montre le schéma fonctionnel complet du système de décodage, y compris le bloc Zynq UltraScale+, le pilote pour le Zmod ADC, le module de contrôle d'acquisition, la BRAM, le contrôleur AXI BRAM pour le stockage des échantillons et les autres blocs AXI.

Des améliorations de vitesse sont possibles

Alors que l'algorithme de Goertzel fonctionne, grâce au RPU, très bien sur l'appareil Zynq UltraScale+, il n'est pas très adapté pour l'utiliser à la périphérie, car il doit acquérir une fenêtre entière pour s'exécuter. Même si l'unité de traitement en temps réel fonctionne à 500 MHz et que le traitement de tous les échantillons prend 60 µs, la fréquence maximale est limitée à 16 kHz.

Il existe plusieurs options pour améliorer les performances. Premièrement, l'algorithme pourrait être exécuté dans la PL, permettant de traiter chaque signal au moment où il est acquis. De plus, l'utilisation d'un filtre coupe-bande avec un détecteur de crête réduira le temps nécessaire au calcul à une fraction de celui requis par l'algorithme de Goertzel. Mais dans ce cas, l'information portant la phase du signal est perdue.

Une autre option consiste à utiliser les deux cœurs RTU sur le Zynq UltraScale+, car ils peuvent être exécutés en mode divisé. Contrairement à DFT, où une décimation dans le temps peut être implémentée, les filtres IIR ont besoin des sorties précédentes pour calculer la suivante. Ici, le délai sera toujours de 60 µs, mais le débit s'améliorera, car la sortie sera mise à jour à deux fois la fréquence.

Sur le site Web de Digilent, un exemple de projet complet est disponible en téléchargement : https://projects.digilentinc.com/pablotrujillojuan/single-tone-detector-with-genesys-zu-and-rtu-728c3f

(*) Mr Pablo Trujillo est un développeur FPGA pour les dispositifs d'électronique de puissance et un spécialiste de la conception de DSP et de contrôle d'électronique de puissance.

Toutes les images de cette page sont la propriété de Mr Pablo Trujillo.