- 1381 views

Crédits (textes et photos): Adam Taylor

Traduction de la page originale: https://www.hackster.io/adam-taylor/high-performance-imaging-ac156d

Choses utilisées dans ce projet:

Composants matériels

- Platine Digilent Genesys ZU

- Capteur vidéo PCAM5

Applications logicielles et services en ligne

- Xilinx Vivado Design Suite

- Xilinx Software Development Kit

Introduction

Le traitement d'images est au cœur de nombreuses applications, de la simple vision embarquée aux véhicules autonomes jusqu'aux drones. Le MPSoC de Xilinx™ avec sa capacité DisplayPort intégrée et la prise en charge de MIPI DPhy dans les Eentrées/Sorties logiques programmables constitue une excellente plate-forme de vision intégrée.

Ces capacités nous permettent de créer une vision embarquée complexe et des systèmes de traitement basés sur la vision qui utilisent l'intelligence artificielle et l'apprentissage automatique.

Dans ce projet, nous allons explorer la mise en place et le fonctionnement d'une chaîne de traitement d'images à l'aide du capteur vidéo PCAM et du port d'affichage. Nous pouvons ensuite ajouter des cœurs IP de synthèse de haut niveau pour poursuivre le traitement de l'image afin de démontrer les capacités de la carte.

Conception logique programmable

Pour commencer avec cette conception, nous devons avoir les fichiers de support de la carte Genesys ZU EG installés dans Vivado. Si nous ne les avons pas, nous pouvons les télécharger à partir d'ici. Installez ces fichiers à l'emplacement suivant dans votre installation Vivado comme indiqué ci-dessous, notez que j'ai placé le dossier entier dedans.

Une fois cette opération terminée, nous sommes prêts à commencer le développement de la conception matérielle.

Dans notre conception, nous allons inclure l'IP suivante:

- Système de traitement Zynq MPSoC - Système de traitement configuré pour activer DisplayPort, I2C et GPIO EMIO

- Sous-système MIPI CSI2 RX - Reçoit le flux MIPI CSI2 du PCAM.

- Sensor Demosaic - Convertissez le format de pixel RAW en un format de pixel RGB.

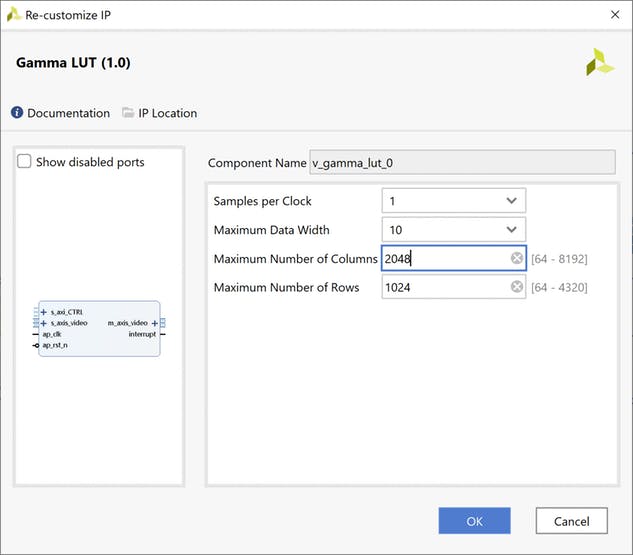

- Gamma LUT - Corrige l'image pour le gamma

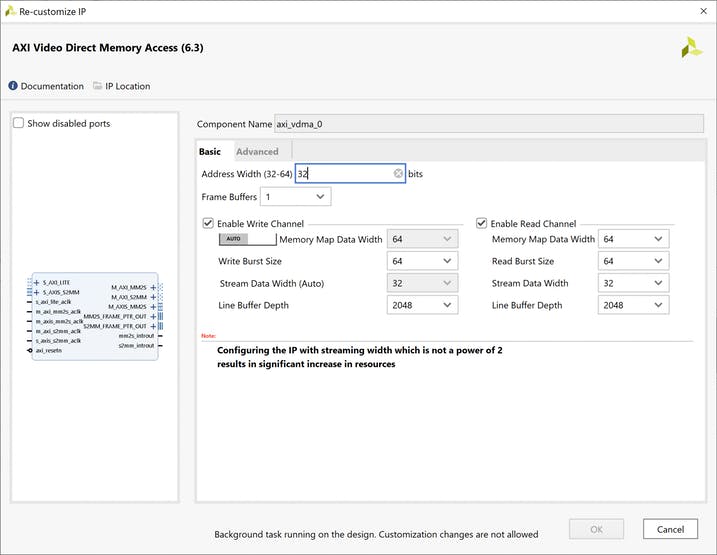

- VDMA - Écrit l'image dans la mémoire DDR du système de processeur

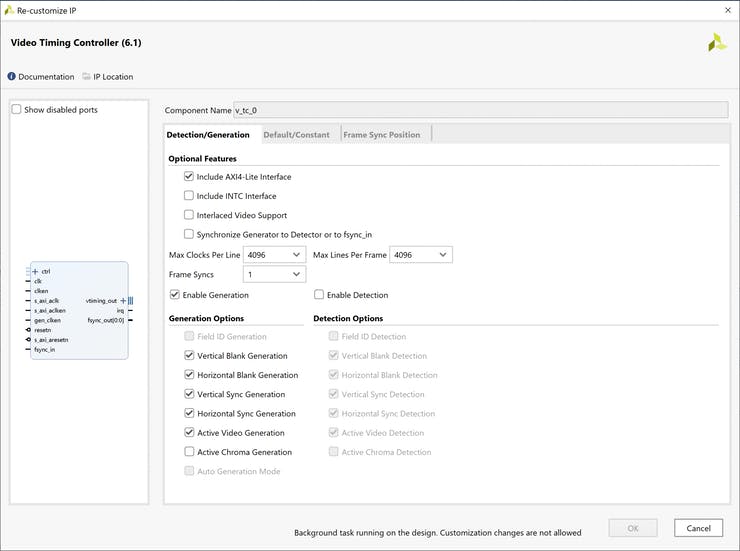

- Générateur de synchronisation vidéo - Génère la synchronisation vidéo de sortie

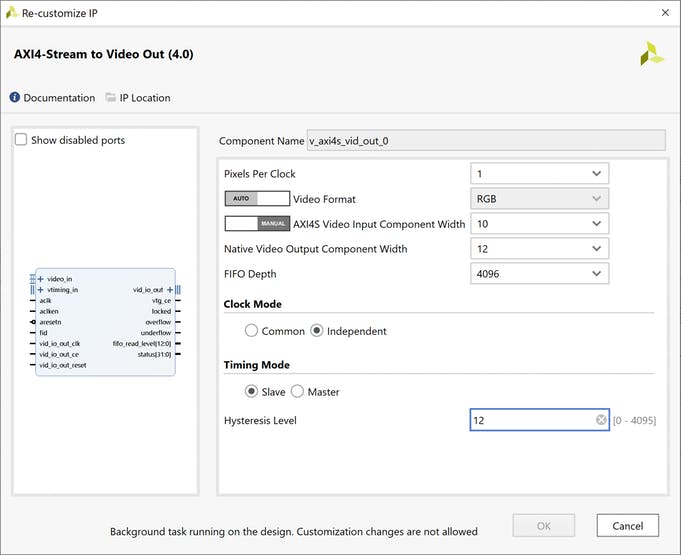

- AXIS vers sortie vidéo - Convertit d'AXI Stream en vidéo parallèle

- Assistants d'horloge - utilisés pour générer l'horloge de pixel vidéo et l'horloge de référence MIPI CSI2

Parallèlement à l'IP, nous devons également prendre en compte l'architecture de synchronisation, pour cette solution, nous implémentons l'approche suivante:

- Horloge AXI - 150 MHz - Ceci est horloge du flux AXI et l'interface AXI lite

- Référence DPHY - 200 MHz - générée par l'assistant d'horloge

- Pixel Clock - 74,25 Mhz - utilisé pour 1280 x 720 à 60 FPS - généré par l'assistant d'horloge

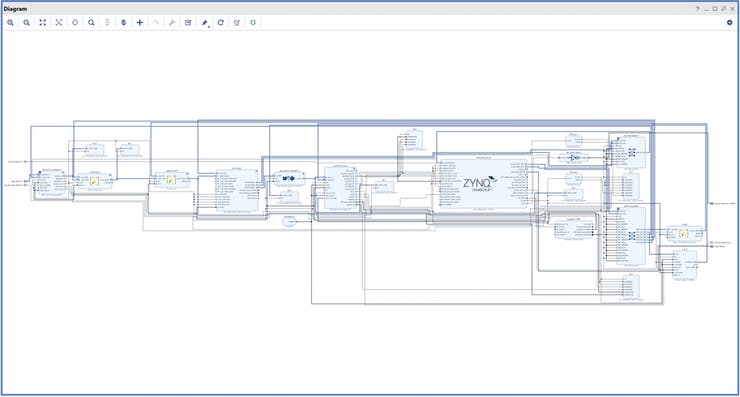

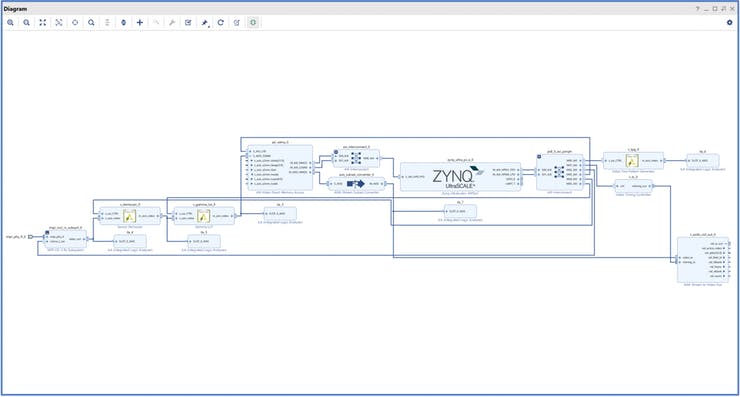

Le schéma fonctionnel terminé devrait ressembler à ci-dessous, avec les cœurs configurés comme indiqué.

La conception complète

Connexions AXI seules

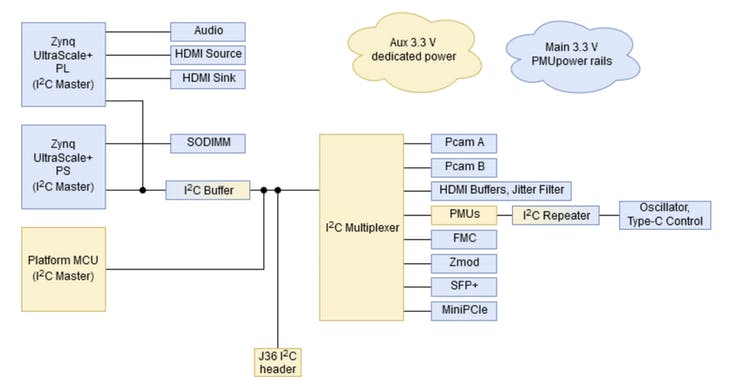

Pour contrôler et configurer le capteur vidéo PCAM5, nous utilisons un port I2C et GPIO, le signal GPIO est utilisé pour activer le capteur PCAM5 et le mettre sous tension. Alors que l'I2C est utilisé pour la configuration du capteur PCAM5 lui-même.

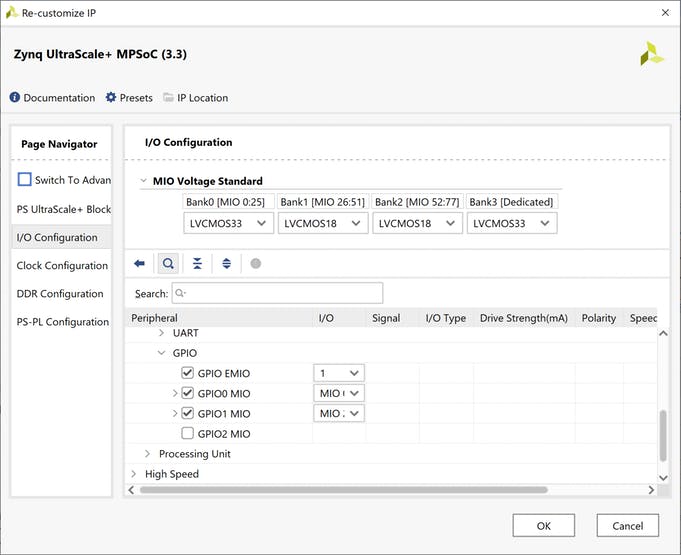

Nous pouvons utiliser le processeur GPIO et l'étendre à la logique programmable pour fournir un seul signal EMIO GPIO. Bien que l'I2C soit fourni par le PS IIC0, il est connecté à un commutateur I2C en tant que tel, nous devons configurer le commutateur dans notre application SW.

Architecture I2C

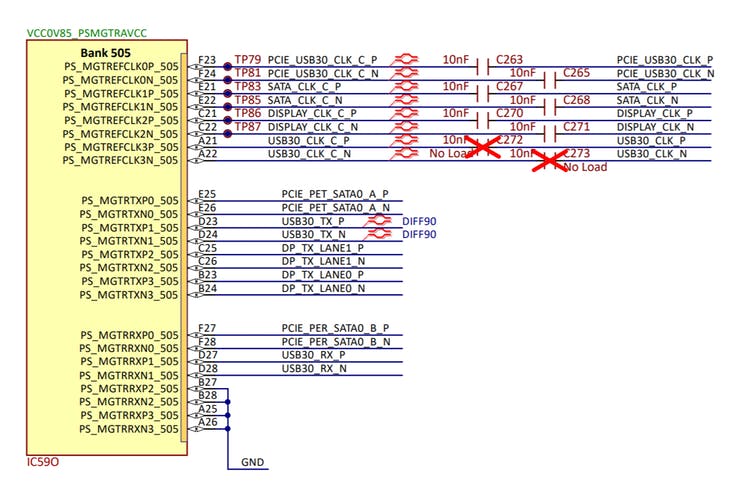

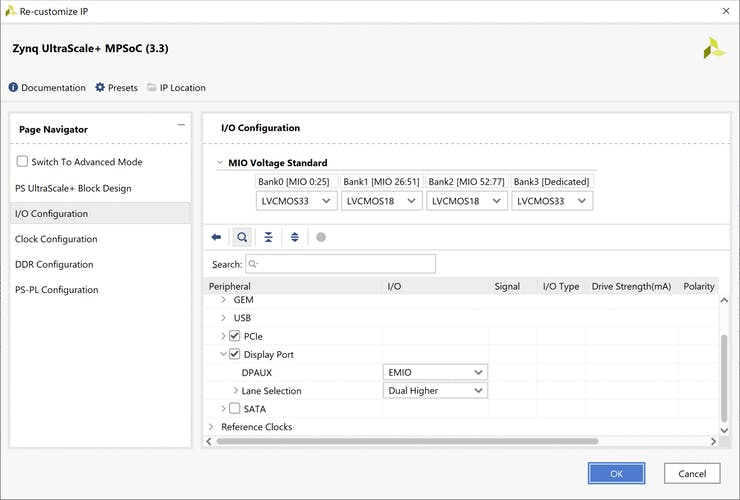

Pour activer le port d'affichage dans le MPSoC, nous devons configurer le périphérique DisplayPort sous la configuration d'E/S. Pour la carte Genesys ZU, cela signifie que nous utilisons les sorties doubles supérieures, car les MGT supérieurs sont utilisés sur la banque 505.

Nous devons également configurer les broches auxiliaires qui sont connectées au PL via EMIO. Cela signifie que nous devons les gérer d'une manière différente que s'ils étaient MIO dans le PS, la broche d'activation de la sortie Aux est active en tant que telle, nous devons utiliser un inverseur sur le signal lorsque nous travaillons avec EMIO.

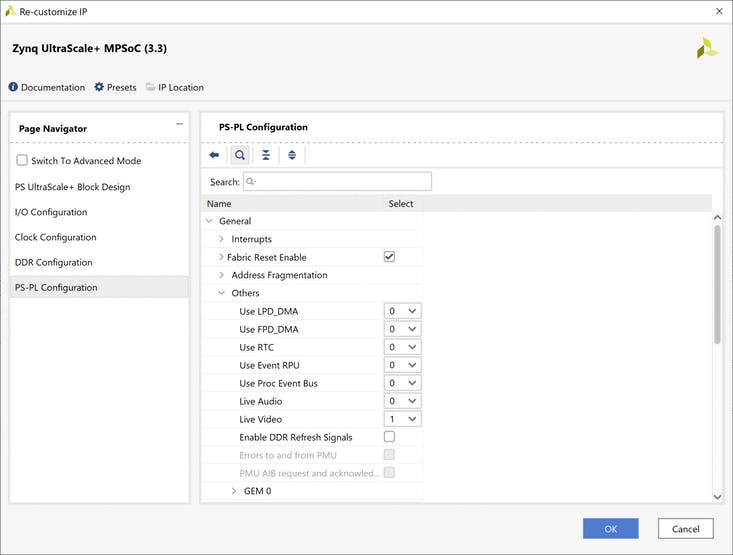

Une fois le DisplayPort configuré, nous sommes en mesure d'activer l'entrée vidéo en direct sur le PL. Ceci est disponible sous les configurations PS-PL.

La configuration finale que nous devons faire est de configurer le GPIO pour fournir un 1 bit EMIO afin que nous puissions allumer et éteindre le module PCAM5.

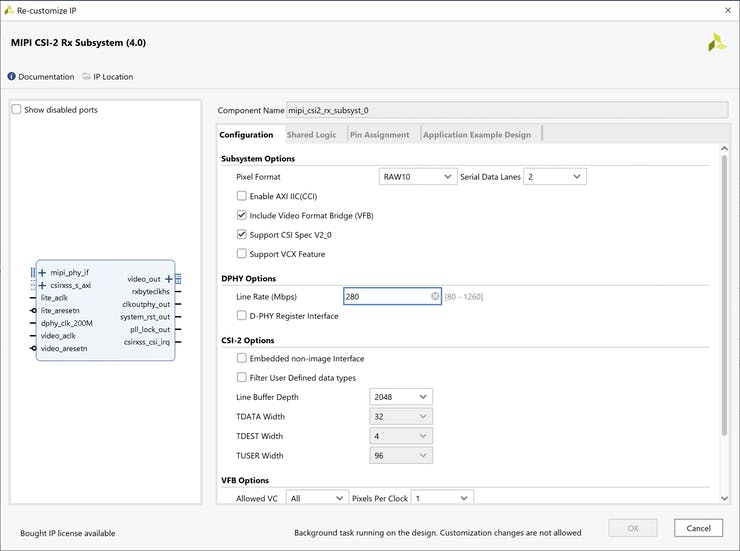

La caméra sera configurée sur l'I2C pour produire une vidéo RAW 10 bits à un débit de 280 Mbps sur deux voies MIPI.

En tant que tel, nous devons configurer le sous-système MIPI CSI-2 RX

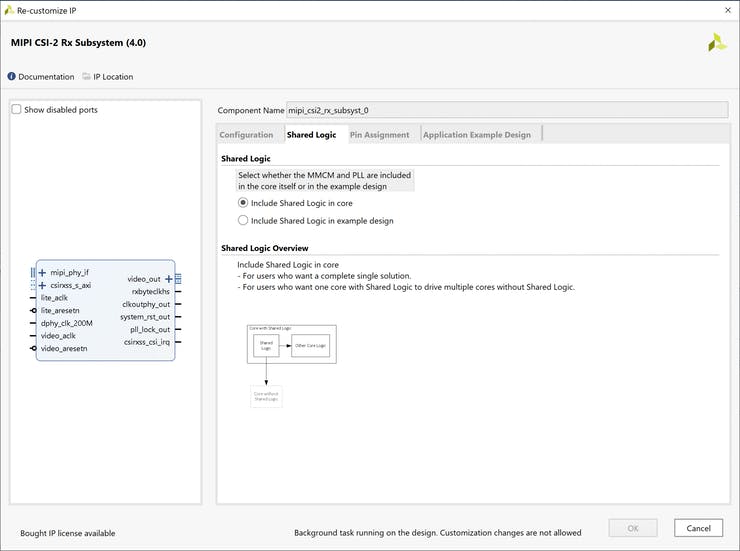

Comme nous n'avons qu'une seule interface MIPI, nous allons configurer le noyau MIPI pour inclure toute la logique partagée. Si nous avions plus d'une interface MIPI sur la même banque, la prochaine interface MIPI serait configurée pour utiliser la logique partagée dans la conception d'exemple.

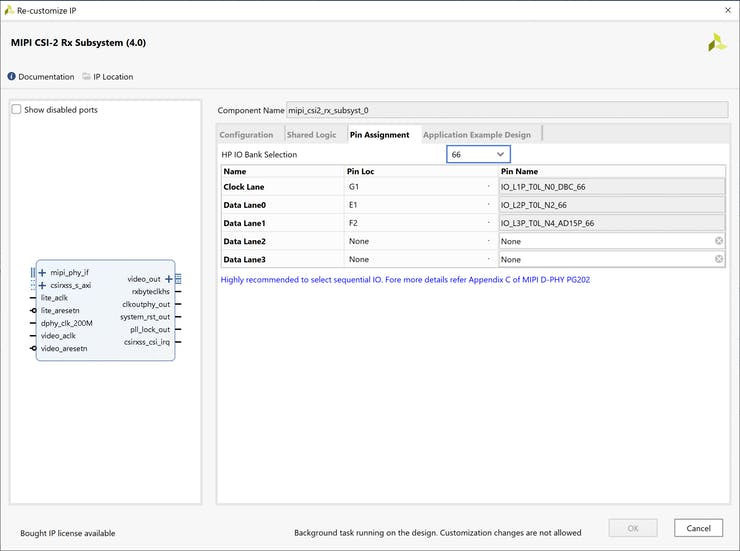

Le réglage final de l'interface MIPI consiste à sélectionner la banque d'E/S et l'attribution des broches pour les voies et horloges MIPI. Comme nous les avons définis ici, nous n'avons pas besoin de les ajouter au fichier XDC qui définit les emplacements des broches.

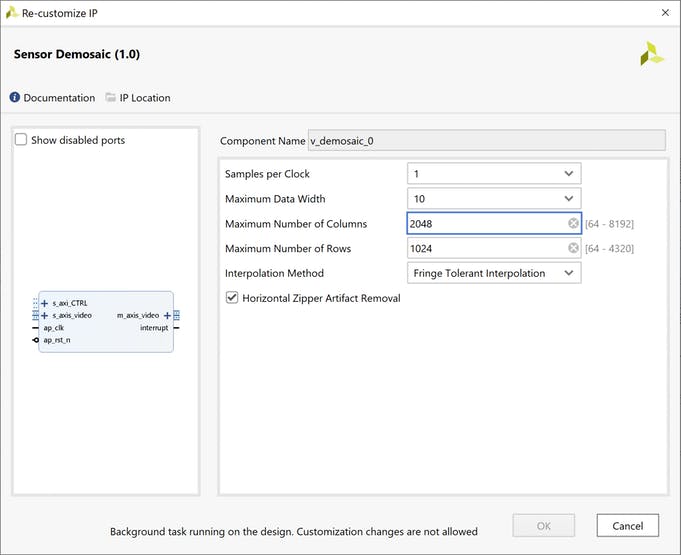

L'étape suivante de la création d'une image utilisable consiste à convertir l'image brute qui contient des informations sur un canal de couleur par pixel.

Dans une image qui contient des éléments rouges, verts et bleus pour chacun, cela s'appelle le débayage et est implémenté par le bloc IP Sensor Demosaic.

Pour notre application, le capteur vidéo PCAM5 produira des pixels au format suivant BGBG / GRGR

Il y a deux fois plus de vert que de rouge et de bleu car nos yeux sont plus sensibles au vert qui est au milieu si le spectre visible est au rouge et au bleu qui sont à chaque extrémité.

La prochaine étape du traitement consiste à implémenter un noyau IP de correction gamma

La dernière étape consiste à insérer un noyau d'accès direct à la mémoire vidéo, ce qui permettra d'écrire les données vidéo sur un dread du PS DDR.

Pour fournir la synchronisation de la vidéo de sortie dans le port d'affichage, nous utilisons le générateur de synchronisation vidéo en mode générateur.

L'étape finale est l'AXIS vers la sortie vidéo IP. Cela prendra le contrôleur de synchronisation vidéo, les signaux de synchronisation et le flux vidéo AXI pour créer une vidéo de sortie avec la synchronisation correcte.

La sortie de celui-ci sera connectée à l'entrée vidéo en direct du port d'affichage.

Cela nécessite un peu de réflexion, l'entrée vidéo en direct pour le a une entrée vidéo 36 bits, 12 bits pour chaque élément du pixel. Nous travaillons avec 10 bits par élément, ce qui en fait 30 bits au total.

Le flux AXIS vers la sortie vidéo augmentera le bloc de sortie, de 30 bits par pixel à 36 bits par pixel en remplissant les LSB.

Pour vous assurer que les canaux de couleur émis par le noyau IP AXIS vers la sortie vidéo sont correctement alignés pour l'entrée vidéo en direct DisplayPort. La façon la plus simple de le faire est dans le flux AXI en utilisant un convertisseur de sous-ensemble AXIS pour changer les canaux de couleur selon les besoins.

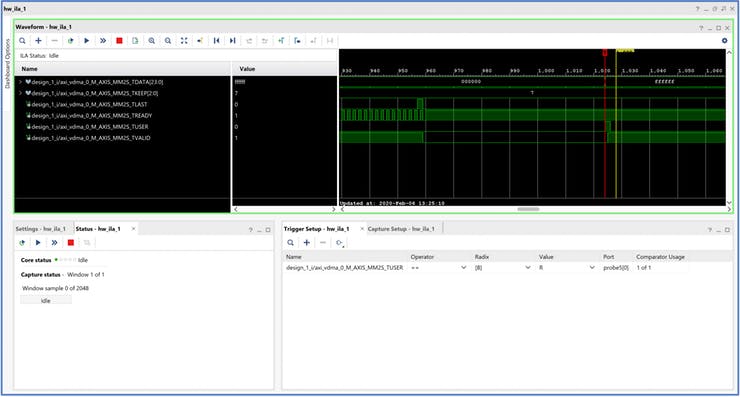

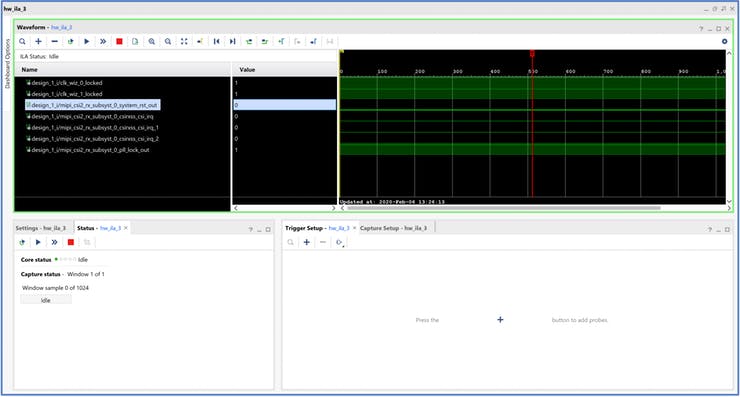

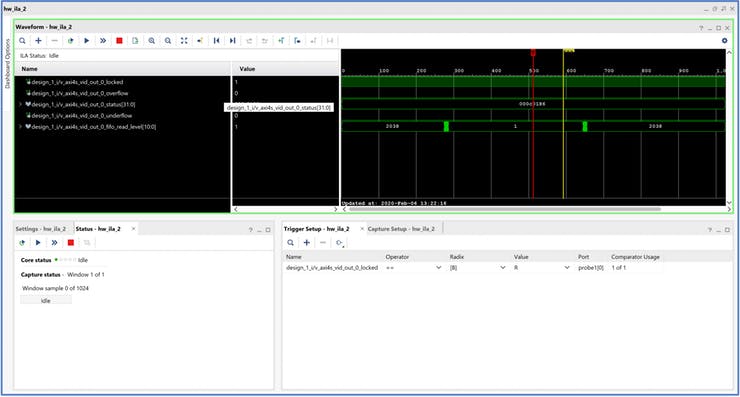

Pour faciliter le débogage et la compréhension de la conception, j'ai également inclus plusieurs analyseurs de logique intégrée dans la conception.

Une fois la conception terminée, nous sommes désormais en mesure de construire la conception matérielle et de mettre en œuvre l'application logicielle à l'aide du SDK.

Développement logiciel

Une fois la conception matérielle terminée, l'étape suivante consiste à écrire le logiciel qui configurera les blocs IP dans la logique programmable. Cette configuration leur permettra de passer à travers la vidéo de sorte qu'elle puisse être affichée sur un moniteur DisplayPort.

En tant que tel, notre logiciel d'application mettra en œuvre les étapes suivantes

1) Configurez le GPIO et activez l'alimentation PCAM5

2) Réglez le mode vidéo 1280 par 720 à 60 FPS et configurez le générateur de modèle de test

3) Configurer le VDMA pour la taille de trame et le stockage en mémoire

4) Configurer le Senso Demosaic

5) Configurer la correction gamma

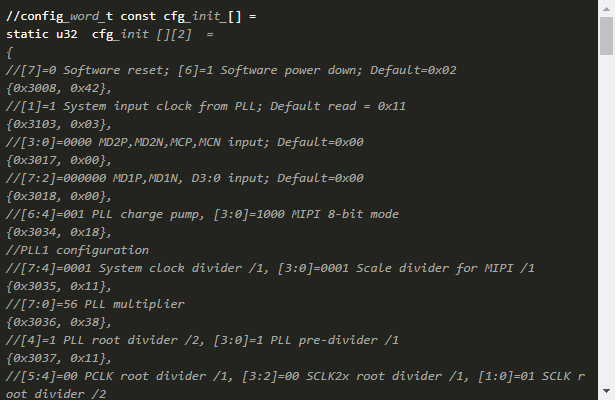

6) Configurer le capteur vidéo PCAM5 à l'aide du lien I2C

7) Activer la lecture et l'écriture des tampons de trame à partir de VDMA

8) Configurer le port d'affichage

Tout comme nous le faisons avec d'autres projets, nous devons importer la spécification matérielle, créer une application et BSP.

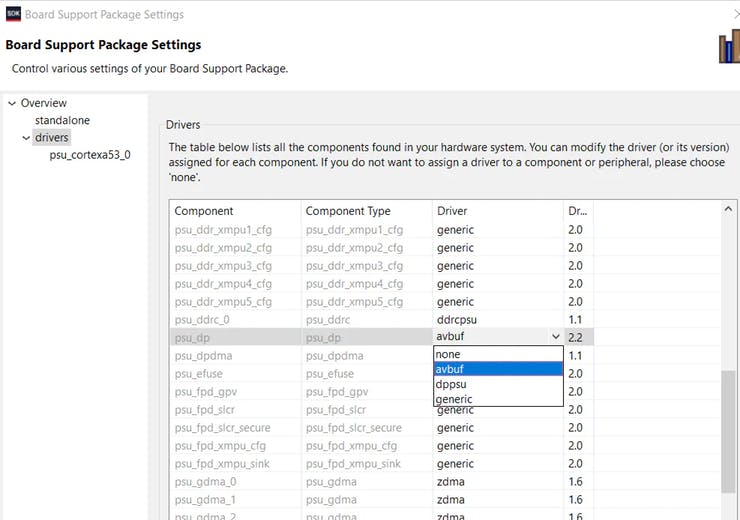

Pour pouvoir utiliser le flux vidéo en direct sur le port d'affichage, nous devons d'abord mettre à jour les paramètres BSP et le générer à nouveau.

Dans les paramètres du BSP, changez avbuf en dppsu et attendez que le BSP soit généré.

Avec le BSP correctement configuré, nous pouvons créer le code d'application. Le BSP fournira toutes les fonctions API nécessaires pour travailler avec les blocs IP dans le PL.

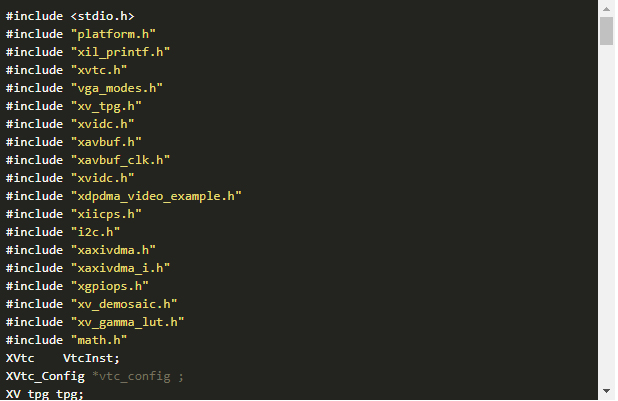

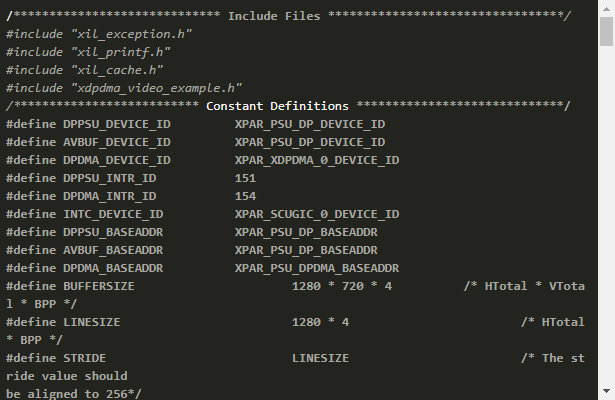

L'application principale est ci-dessous: visualisez les listing complets sur le site: https://www.hackster.io/adam-taylor/high-performance-imaging-ac156d

Entête avec la configuration I2C

Le fichier de configuration du port d'affichage

Essai

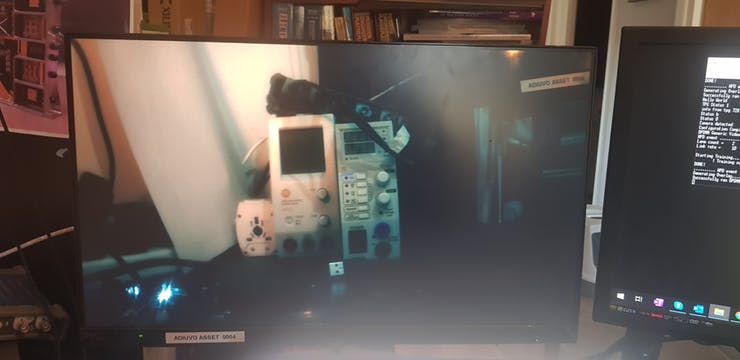

Une fois l'application terminée, nous pouvons créer une configuration de débogage et télécharger le fichier bit et exécuter le logiciel d'application.

Nous devrions voir une image sur le moniteur, mais nous avons également les ILA qui peuvent être examinés. Celles-ci montrent que l'ILA affichera le flux vidéo d'entrée, tel qu'il est reçu du noyau IP MIPI CSI-2 et du VDMA.

AXIS transfère des trames vidéo en utilisant les signaux de bande latérale Tuser et Tlast. Tuser a indiqué le début d'une nouvelle trame, tandis que Tlast indique la fin d'une ligne.

Le troisième IL surveille le flux AXI vers la sortie vidéo, ce qui nous permet de surveiller le signal verrouillé sur la sortie.

Lorsque tout cela fonctionne, vous pourrez voir la sortie des images du capteur vidéo.

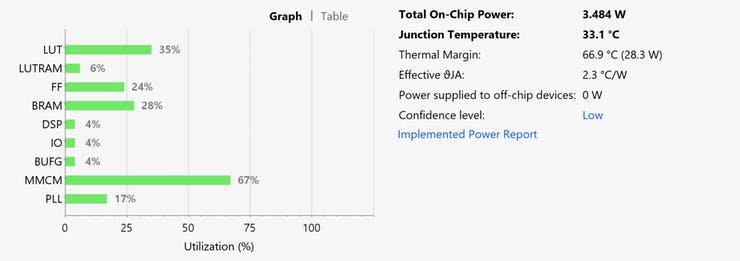

L'utilisation finale des ressources de la solution est indiquée ci-dessous, nous avons beaucoup de place pour mettre en œuvre des algorithmes intéressants

Le code source est disponible ici.

Voir les projets précédents ici.

Des informations supplémentaires sur le développement Xilinx FPGA / SoC sont disponibles chaque semaine sur MicroZed Chronicles.

Crédits (textes et photos): Adam Taylor

Traduction de la page originale: https://www.hackster.io/adam-taylor/high-performance-imaging-ac156d